Overview

The Ultra-Low Power Embedded Processor, also known as the Sensor Network Asynchronous Processor (SNAP), is intended for use in a variety of low-power embedded applications. One potential application is using SNAP as a sensor mote processor, but the intent is as a general-purpose embedded processor which can interface with a multitude of different systems such as radios and GPS receivers. The original processor was designed in 2003 by the Asynchronous VLSI and Architecture Group.

Details

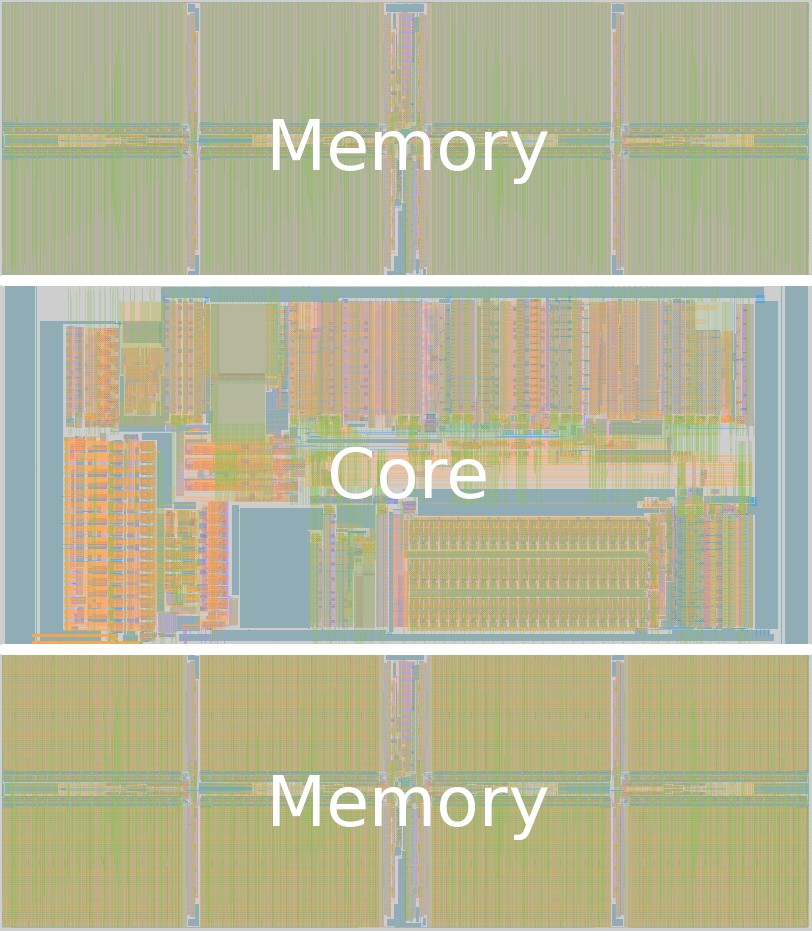

The 2011 revision was designed by Carlos Tadeo Ortega Otero and includes several significant redesigns of major subsystems. The complete system can be seen below. It measures 860um by 1020um in a 90nm process. The logical system architecture is that of an event-driven processor, which "wakes up" in response to an event, computes, and then returns to a low power or sleep state.

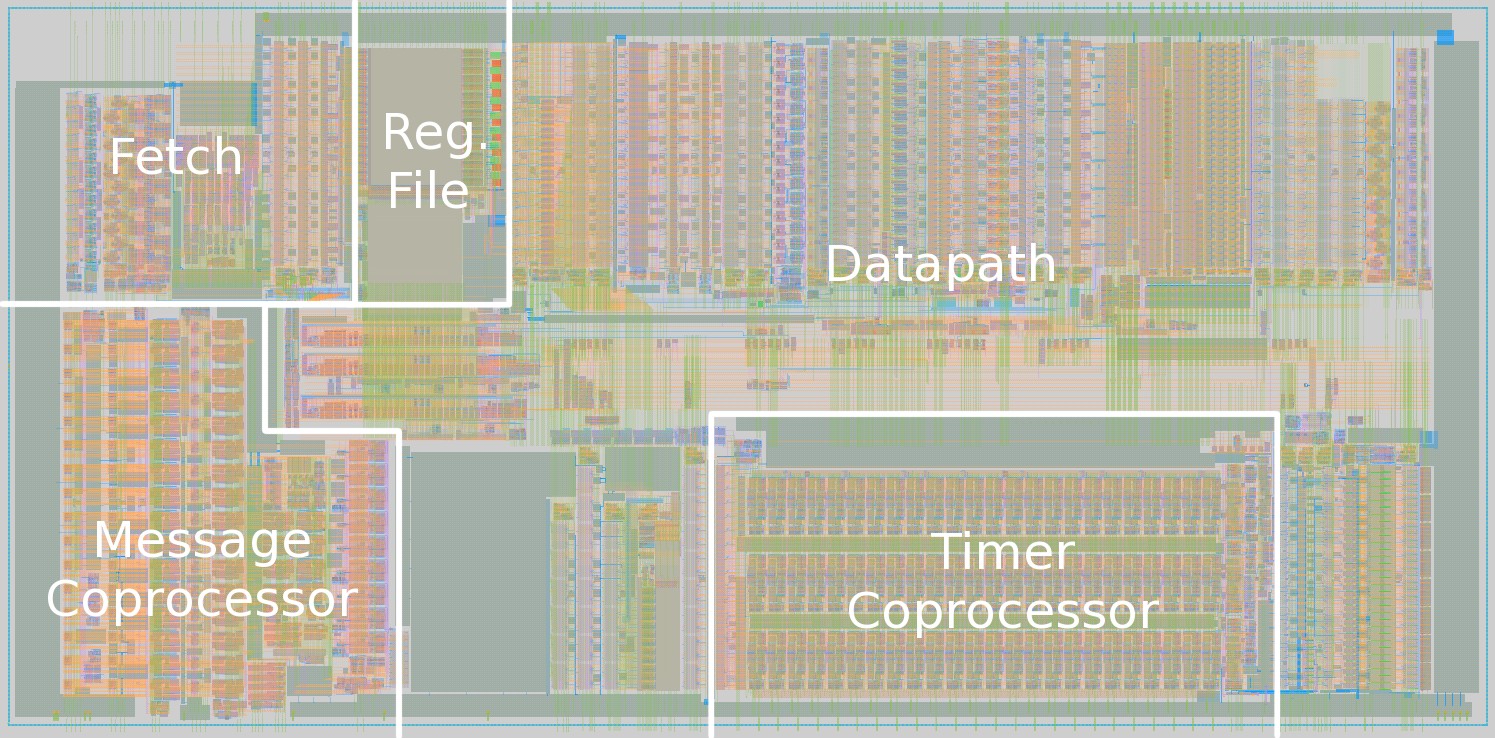

The Fetch, Register File, and Datapath can all be seen below in the layout of the SNAP core, sans memories. The Datapath includes the instruction decode logic, as it has been distributed throughout the core.

Of particular interest are the coprocessors. The Timer Coprocessor is a series of configurable counters to handle event timing, interrupts, and similar cases for the event-driven architecture. The Message Coprocessor, which includes an SPI bus interface, essentially is a message passing FIFO interface to other systems such as the aforementioned radios, GPS, and even the SPI interface.

My contributions to the 2011 SNAP iteration include design work in the SPI interface, VLSI layout of significant portions of both coprocessors as well as the fetch and datapath. Core team members for the 2011 effort, lead by Carlos Tadeo Ortega Otero, were Benjamin Hill and Robert Karmazin.

Related Publications

-

Clinton Kelly IV, Virantha Ekanayake, and Rajit Manohar. SNAP: A Sensor Network Asynchronous Processor. ASYNC 2003

-

Virantha Ekanayake, Clinton Kelly IV, and Rajit Manohar. An Ultra-low-power Processor for Sensor Networks. ASPLOS 2004

-

Virantha Ekanayake, Clinton Kelly IV, and Rajit Manohar. BitSNAP: Dynamic Significance Compression for a Low Power Sensor Network Asynchronous Processor. ASYNC 2005

-

Yao-Win Hong, et al. Dense Sensor Networks are also Energy-efficient. MILCOM 2005

-

Filipp Akopyan, Rajit Manohar, and A. Apsel. A level-crossing Flash Asynchronous Analog-to-Digital Converter. ASYNC 2006

-

Carlos Tadeo Ortega Otero, Jonathan Tse, and Rajit Manohar. Static Power Reduction Techniques for Asynchronous Circuits. ASYNC 2010

-

Carlos Tadeo Ortega Otero, Jonathan Tse, Robert Karmazin, Benjamin Hill, and Rajit Manohar. ULSNAP: An Ultra-Low Power Event-Driven Microcontroller for Sensor Network Notes. ISQED 2014